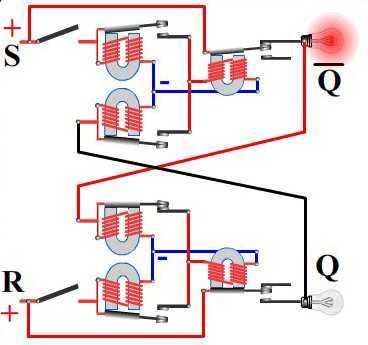

Триггер собранный на реле

Простейшими схемами являются RS триггеры. Буквы S и R означают английские слова set и reset – «установка» и «сброс» соответственно. Этими буквами обозначаются два входа устройства, один из которых (S) при поступлении сигнала приводит к изменению состояния триггера, а второй (R) – сбрасывает элемент в стартовое состояние. Анимация ниже иллюстрирует принцип работы триггерной схемы, собранной из нескольких электромагнитных реле.

Принцип работы тригерной схемы

В начальном состоянии система находится в положении 0 (логический ноль или «FALSE»), о чем свидетельствует негорящая лампочка на прямом выходе Q. Инверсный выход, обозначаемый с черточкой наверху, соответственно, показывает уровень логической единицы (1), поэтому лампа на нем горит.

При замыкании ключа S, что символизирует подачу на вход единичного сигнала, на реле подается положительное напряжение и происходит переход триггера в логическое состояние 1 или «TRUE», соответственно, лампочка на прямом выходе загорается, а на инверсном гаснет. Затем происходит сброс системы путем замыкания ключа R, триггер переходит в стартовое состояние. Однако до того момента, как будет нажата кнопка сброса, он продолжает сохранять то состояние, в которое его привело замыкание ключа S.

Симметричный триггер. Принцип работы

Рис.1 Схема симметричного триггера и диаграмма.

На рис.1 изображена схема статического симметричного триггера на транзисторах типа p-n-p и диаграмма напряжений на коллекторах и базах. В каждом из состояний устойчивого равновесия один из транзисторов открыт (в режиме насыщения), другой закрыт (в режиме отсечки).

Пусть транзистор T1 открыт, а Т2 закрыт. При этом потенциал на коллекторе транзистора Т1 близок к нулю; а на коллекторе Т2 близок к -Ek. Из базы транзистора T1 через резистор R1″ отбирается ток, удерживающий этот транзистор в состоянии насыщения.

Транзистор Т2 закрыт, так как на его базе образуется положительное напряжение смещения за счет источника Есм Конденсатор С1′ практически разряжен, а С1″ заряжен до напряжения близкого к Ek. В связи с тем, что коэффициент усиления по току транзисторов, находящихся в режиме отсечки и насыщения, равен нулю, общее усиление в петле обратной связи также равно нулю. Этим обеспечивается устойчивость описанного состояния.

Переход триггера из одного устойчивого состояния в другое (т.е. его переключение или опрокидывание) осуществляется путем воздействия внешнего запускающего импульса на базы или коллекторы транзисторов. (Подробнее о запуске триггера см. ниже.) Причем параметры запускающего сигнала должны обеспечивать вывод транзисторов в активный режим работы, когда восстанавливается усиление по току у транзисторов и в течение времени опрокидывания действует положительная обратная связь между ключами.

После опрокидывания на коллекторе транзистора T1 устанавливается отрицательный потенциал, близкий к -Ek, а на коллекторе T2 потенциал, близкий к нулю. Конденсатор С1′ заряжается, a С1″ разряжается, и на базе транзистора T1, устанавливается положительный потенциал, примерно равный Есм, а на базе T2 небольшой отрицательный потенциал (см. диаграмму). Новое устойчивое состояние триггера сохраняется до прихода очередного запускающего импульса.

Физические реализации триггеров

Базовый элемент создают из полупроводниковых приборов, используя современные технологические процессы для миниатюризации функциональных изделий.

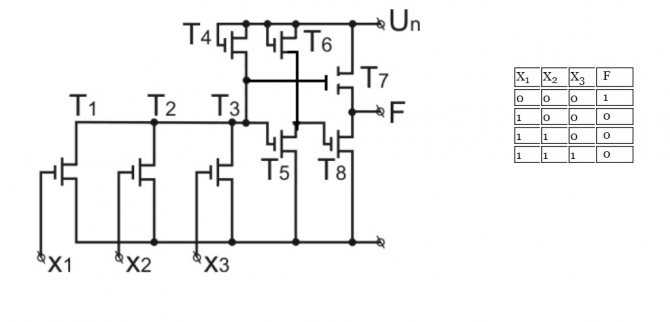

Логический элемент на МОП транзисторах

Триггеры с тиристорами

Для повышения мощности подключаемой нагрузки можно собрать триггер с применением тиристоров. К управляющему электроду присоединяют вход S, к затвору – R. Для поддержания постоянного напряжения на аноде подойдет транзистор, включенный в соответствующую цепь.

Триггеры на релейно-контакторной базе

Несмотря на общие тенденции миниатюризации, вполне допустимо создать функциональный триггер из реле. Подобные решения, в частности, применяют для защиты цепей питания при включении мощных электроприводов.

8.4 Синхронный Т — триггер (счетный триггер)

Счетные триггеры (или Т-триггеры) реализованы только в виде схем, тактируемых срезом синхроимпульса. В триггерах этого типа имеется только один вход – счетный тактирующий вход Т (рис. 8.9).

Рисунок 8.9 – Условное обозначение (а) и таблица состояний (б) Т-триггера

Таким образом, при или триггер остается в исходном состоянии. При переходе сигнала состояние триггера инвертируется.

Переключение триггера происходит по срезу тактового импульса, т.е. частота выходных импульсов в 2 раза меньше частоты входных на линии Т (рис. 8.10). Т-триггеры применяют в счетчиках.

Рисунок 8.10 – Временная диаграмма работы Т-триггера.

Логическое уравнение Т-триггера имеет такой вид:

.

Это выражение означает, что выход триггера принимает значение, инверсное по отношению к его состоянию до появления среза входного импульса T.

Универсальный JK-триггер

УниверсальныйJK-триггер – это логическая комбинация RS — и Т-триггеров. Это понятие означает, что при некоторых значениях входных сигналов устройство работает как RS-триггер, а при некоторых значениях входов – как T-триггер. Таблица состояний JK-триггера представлена на рис. 8.11.

Рисунок 8.11 – Таблица состояний JK-триггера

JK-триггеры в интегральном исполнении обычно имеют три сгруппированных по И (&) входа (установка триггера в “1”) и аналогично сгруппированных И (&) входа (установка триггера в “0”). Эти входы синхронизированы по срезу сигнала на входе С. Кроме того, такие триггерные устройства имеют статические входы предустановки и , работающие в инверсной логике. Типовое условное обозначение JK-триггера в интегральном исполнении представлено на рис. 8.12-а, пример временная диаграмма его работы – на рис. 8.12-б.

Рисунок 8.12 – Обозначение (а) и временная диаграмма (б) для JK-триггера

Тактовые импульсы С могут быть и периодическими, и единичными. Эти импульсы являются стробом записи бита информации в триггер по входам J и К.

JK-триггеры в интегральном исполнении являются универсальными устройствами, на основе которых могут быть построены основные виды триггеров. При построении триггеров различных типов за счет внешних соединений исключаются из таблицы состояний JK-триггера некоторые комбинации входных сигналов, несущественные для создаваемого триггера (рис. 8.11).

Для получения асинхронного RS-триггера достаточно использовать входы статической предустановки, а на все остальные входы статически подать “0”. Такое подключение показано на рис. 8.13-а.

При построении синхронного RS-триггера группы входов J и Kсоединены вместе, чтобы обеспечить одновременное поступление сигналов R и Sна группы одноименных входов (8.13-б).

Для построения счетного Т-триггера (рис. 8.13-в) необходимо исключить все входные комбинации, кроме . Это достигается статической одновременной подачей «1» на все входы J и K.

Для построения схемы D-триггера (рис. 8.13-г) нужно исключить входные комбинации и , а также сформировать только один информационный вход устройства. При этом учитывается, что в оставшихся комбинациях входы J и K работают в противофазе. Это достигается за счет включения инвертора. Функциональное назначение входа D(вход данных)рассматривается относительно входа J.

Рисунок 8.13 – Построение различных триггеров на основе JK-триггера: а) асинхронный RS-триггер; б) синхронный RS-триггер с предустановкой; в) счетный Т-триггер; г) D-триггер.

Группы входов J и Kиспользуются индивидуально (отдельно каждая линия) для построения синхронных счетчиков (см. Модуль 1 – Тема 10).

Предыдущая статья «8.3 D-триггер (триггер данных)»

Следующая статья >> «9.1 Ввод аналоговых сигналов в МК на основе частотно-импульсной модуляции»

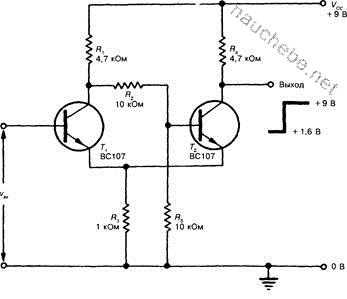

Триггер Шмитта принцип действия

является схемой с двумя устойчивыми состояниями, но ее состояние определяется уровнем напряжения на входе. Он применяется как схема определения уровня сигнала, а также как средство преобразования синусоидального сигнала в прямоугольный сигнал с малым временем нарастания и спада. Типичная схема триггера Шмитта, составленная из дискретных компонентов, показана на рис. 12.15.

При нулевом напряжении на входе транзистор Тх заперт, и поэтому транзистор Т2 находится в насыщении; его ток базы течет по резисторам Rxи Rr Пренебрегая разностью потенциалов между коллектором и эмиттером транзистора Т2, можно считать, что напряжение питания 9 В распределено

Рис. 12.15. .

между резистором R3 в эмиттере и резистором R4 в коллекторе. На резисторе R3 упадет 1,6 В, а на резисторе R4 — 7,4 В; разности потенциалов пропорциональны сопротивлениям резисторов, составляя в сумме 9 В. Поэтому потенциал эмиттера транзистора Тх равен 1,6 В, и напряжение коллектора транзистора Т2 находится примерно на том же уровне. Когда входное напряжение увеличивается до значения vbx = 2 В, через транзистор Тх начинает протекать ток, вызывающий падение напряжения на коллекторной нагрузке Rv отбирая ток базы у транзистора Т2. По мере того как падает эмиттерный ток транзистора Т2, уменьшается напряжение на общей эмиттерной нагрузке R3, открывая транзистор Тх еще быстрее. Эта регенеративная положительная обратная связь продолжает действовать до тех пор, пока транзистор Тх не попадет в насыщение, а транзистор Т2 не закроется; выходное напряжение становится при этом равным +9 В.

Если vbx теперь уменьшается, то коллекторный ток транзистора Тх постепенно падает. В это время, однако, начинает действовать дополнительный фактор: в игру вступает эмиттерный повторитель и напряжение на эмиттере транзистора 7j падает вместе с входным напряжением до тех пор, пока напряжение на коллекторе транзистора Тх не поднимется настолько, что станет открываться транзистор Т2. Когда в транзисторе Т2 начинает увеличиваться ток эмиттера, он вызывает быстрый регенеративный процесс: дополнительное падение напряжения на резисторе R3 помогает запиранию транзистора Тх, поднимая потенциал его эмиттера. Как только транзистор Тх полностью закроется, напряжение на его коллекторе поднимется до напряжения источника питания, полностью открывая транзистор Т2.

Функционирование эмиттерного повторителя, который вступает в действие, когда vbx уменьшается, является причиной гистерезиса в триггере Шмитта: триггер выключается при меньшем напряжении, чем включается. В рассмотренной схеме гистерезис мал и составляет приблизительно 0,6 В, но его можно изменить, выбирая другие отношения Rx: R4 и R^: Ry

В базу транзистора Тх, конечно, течет некоторый ток, когда схема переключается. Если это нежелательно, то на место транзистора Тх можно непосредственно поставить я-канальный полевой транзистор, такой как 2N3819, обеспечивающий схеме большое входное сопротивление, обычно присущее схемам на полевых транзисторах.

является идеальной схемой для стыковки медленно меняющихся сигналов с логическими схемами, которым требуются сигналы с малым временем нарастания и спада. Для таких применений удобна ИС 7413, являющаяся триггером Шмитта в интегральном исполнении (аналог 555TJI1. — Примеч. перев.); дальнейшее обсуждение вопросов, относящихся к применению этой ИС, см. в разд. 13.14.

Литература: М.Х.Джонс, Электроника — практический курс Москва: Техносфера, 2006. – 512с. ISBN 5-94836-086-5

Tweet Нравится

- Предыдущая запись: ВЫБОР ТРАНЗИСТОРА

- Следующая запись: Принцип изменения сопротивления

Чем отличается ток от напряжения? (2)

Связь тока и напряжения (0)

ИСТОЧНИК ПИТАНИЯ ДЛЯ АВТОМОБИЛЬНОГО РАДИОПРИЕМНИКА (0)

ЗАРЯДНОЕ УСТРОЙСТВО ДЛЯ АККУМУЛЯТОРА (0)

ЗАРЯДНОЕ УСТРОЙСТВО ДЛЯ ЛИТИЙ-НОННОГО ЭЛЕМЕНТА КОНТРОЛЛЕР ЗАРЯДНОГО УСТРОЙСТВА (0)

ОГРАНИЧИТЕЛЬ ЗАРЯДНОГО TOKA АККУМУЛЯТОРА (0)

ЗВУКОВОЕ УСТРОЙСТВО ДЛЯ ОХРАНЫ МОТОЦИКЛА (0)

Классификация

Энергия конденсатора

Изделия этой категории разделены на две основные группы по принципу сигналов управления. В первой – формируется заданная последовательность выходных сигналов, если установлено состояние «1». После переходе в «0» генерация прекращается. Вторая – способна переключать выходное напряжение соответствующим образом. Как правило, «1» примерно соответствует уровню источника питания.

Также триггеры различают по следующим параметрам:

- синхронность рабочих циклов;

- статические (динамические) способы управления;

- сложность логических схем;

- одно,- или двухступенчатые.

Триггеры на логических элементах и на операционном усилителе

Для реализации статических триггеров хорошо подходит схема усилителя с двумя каскадами. Связь между ними организуют прямую либо с ограничительными резисторами в соответствующих цепях.

Триггер на логических элементах

Триггер на логических элементах

Триггер (Trigger) Шмитта

Изделия этой категории могут быть созданы с применением разной элементной базы. В данном разделе рассмотрен триггер Шмитта на транзисторах. Он управляется изменением аналогового сигнала. В зависимости от уровня напряжения, выполняется переключение состояния памяти в соответствующее положение «0» или «1».

Триггер Шмидта на транзисторах с подключенной нагрузкой

Триггер Шмидта на транзисторах с подключенной нагрузкой

Способы повышения быстродействия симметричного триггера

Быстродействие триггера как устройства, основанного на транзисторных ключах, определяется скоростью переключения выбранных транзисторных ключей.

Следовательно, основными методами повышения быстродействия триггера являются: 1) применение высокочастотных транзисторов; 2) устранение (или уменьшение) задержки выключения, обусловленной рассасыванием неосновных носителей в базе насыщенного транзистора; 3) применение специальных способов, уменьшающих время установления напряжения на коллекторах и ускоряющих конденсаторах.

С целью сокращения времени рассасываний неосновных носителей в базе применяются ненасыщенные ключи, например, за счет введения нелинейной отрицательной обратной связи через диоды Дос(рис.5). Ненасыщенный триггер обладает более высокой чувствительностью к запускающим импульсам, с чем связано снижение его помехоустойчивости.

Действие нелинейной обратной связи состоит в следующем. При отпирании транзистора входным током отрицательный потенциал его коллектора уменьшается. Когда он сравняется с потенциалом в точке «а», диод открывается, и часть входного тока замыкается через диод. Транзистор не входит в насыщение.

Для сокращения фронтов выходного напряжения (главным образом отрицательного фронта) может быть применена фиксация минимального коллекторного потенциала через диод Дф (рис.6). При отпертом транзисторе диод Дф заперт. При запирании транзистора отрицательное напряжение на его коллекторе растет, и когда достигает значения Еф, диод отпирается и фиксирует коллекторный потенциал на уровне — Дф. Как видно из рисунка, длительность отрицательного фронта существенно уменьшается, а положительного, как более крутого в первоначальной стадии, изменяется мало.

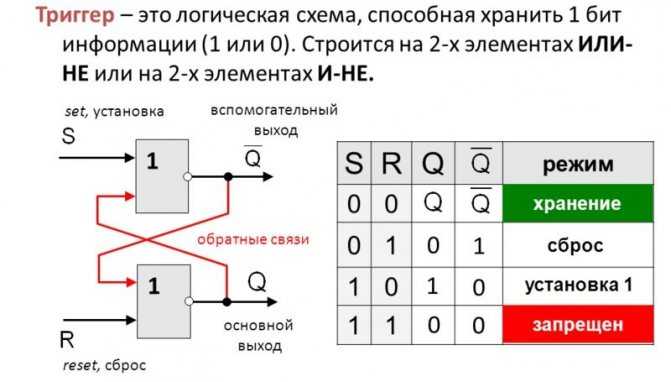

Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений).

Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер. RS-триггер имеет два логических входа:

- R – установка 0 (от слова reset);

- S – установка 1 (от слова set).

RS-триггер имеет два выхода:

- Q – прямой;

- Q- обратный (инверсный).

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью.

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль – со входа R, другой – с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента.

Будет интересно Что такое термопара: об устройстве простыми словами

Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в “0”. Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния. Для описания работы триггера используют таблицу состояний (переходов). Обозначим:

- Q(t) – состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- Q(t+1) – состояние триггера после изменения на входах R и S.

Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения |

| Режим хранения информации R=S=0 | ||||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=1 | ||

| 1 | 1 | 1 | ||

| 1 | Режим установки нуля R=1 | |||

| 1 | 1 | |||

| 1 | 1 | * | R=S=1 запрещённая комбинация | |

| 1 | 1 | 1 | * |

RS-триггер можно построить и на элементах “И-НЕ” (рисунок 2.2).

Входы R и S инверсные (активный уровень “0”). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов “0”. Комбинация R=S=0 является запрещённой.

Таблица переходов RS триггера в базисе “2И-НЕ”

| R | S | Q(t) | Q(t+1) | Пояснения |

| * | R=S=0 запрещённая комбинация | |||

| 1 | * | |||

| 1 | Режим установки нуля R=0 | |||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=0 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | Режим хранения информации R=S=1 | ||

| 1 | 1 | 1 | 1 |

Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется “опасные гонки”), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала).

Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера приведена.

Таблица переходов синхронного RS-триггера

| R | S | C | Q(t) | Q(t+1) | Пояснения |

| 1 | Режим хранения информации R = S = 0 | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы S =1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим установки нуля R=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | * | R = S = 1 запрещённая комбинация | |

| 1 | 1 | 1 | 1 | * |

В таблице 2.3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

Триггер Шмитта принцип действия

является схемой с двумя устойчивыми состояниями, но ее состояние определяется уровнем напряжения на входе. Он применяется как схема определения уровня сигнала, а также как средство преобразования синусоидального сигнала в прямоугольный сигнал с малым временем нарастания и спада. Типичная схема триггера Шмитта, составленная из дискретных компонентов, показана на рис. 12.15.

При нулевом напряжении на входе транзистор Тх заперт, и поэтому транзистор Т2 находится в насыщении; его ток базы течет по резисторам Rxи Rr Пренебрегая разностью потенциалов между коллектором и эмиттером транзистора Т2, можно считать, что напряжение питания 9 В распределено

Рис. 12.15. .

между резистором R3 в эмиттере и резистором R4 в коллекторе. На резисторе R3 упадет 1,6 В, а на резисторе R4 — 7,4 В; разности потенциалов пропорциональны сопротивлениям резисторов, составляя в сумме 9 В. Поэтому потенциал эмиттера транзистора Тх равен 1,6 В, и напряжение коллектора транзистора Т2 находится примерно на том же уровне. Когда входное напряжение увеличивается до значения vbx = 2 В, через транзистор Тх начинает протекать ток, вызывающий падение напряжения на коллекторной нагрузке Rv отбирая ток базы у транзистора Т2. По мере того как падает эмиттерный ток транзистора Т2, уменьшается напряжение на общей эмиттерной нагрузке R3, открывая транзистор Тх еще быстрее. Эта регенеративная положительная обратная связь продолжает действовать до тех пор, пока транзистор Тх не попадет в насыщение, а транзистор Т2 не закроется; выходное напряжение становится при этом равным +9 В.

Если vbx теперь уменьшается, то коллекторный ток транзистора Тх постепенно падает. В это время, однако, начинает действовать дополнительный фактор: в игру вступает эмиттерный повторитель и напряжение на эмиттере транзистора 7j падает вместе с входным напряжением до тех пор, пока напряжение на коллекторе транзистора Тх не поднимется настолько, что станет открываться транзистор Т2. Когда в транзисторе Т2 начинает увеличиваться ток эмиттера, он вызывает быстрый регенеративный процесс: дополнительное падение напряжения на резисторе R3 помогает запиранию транзистора Тх, поднимая потенциал его эмиттера. Как только транзистор Тх полностью закроется, напряжение на его коллекторе поднимется до напряжения источника питания, полностью открывая транзистор Т2.

Функционирование эмиттерного повторителя, который вступает в действие, когда vbx уменьшается, является причиной гистерезиса в триггере Шмитта: триггер выключается при меньшем напряжении, чем включается. В рассмотренной схеме гистерезис мал и составляет приблизительно 0,6 В, но его можно изменить, выбирая другие отношения Rx: R4 и R^: Ry

В базу транзистора Тх, конечно, течет некоторый ток, когда схема переключается. Если это нежелательно, то на место транзистора Тх можно непосредственно поставить я-канальный полевой транзистор, такой как 2N3819, обеспечивающий схеме большое входное сопротивление, обычно присущее схемам на полевых транзисторах.

является идеальной схемой для стыковки медленно меняющихся сигналов с логическими схемами, которым требуются сигналы с малым временем нарастания и спада. Для таких применений удобна ИС 7413, являющаяся триггером Шмитта в интегральном исполнении (аналог 555TJI1. — Примеч. перев.); дальнейшее обсуждение вопросов, относящихся к применению этой ИС, см. в разд. 13.14.

Литература: М.Х.Джонс, Электроника — практический курс Москва: Техносфера, 2006. – 512с. ISBN 5-94836-086-5

Tweet Нравится

- Предыдущая запись: ВЫБОР ТРАНЗИСТОРА

- Следующая запись: Принцип изменения сопротивления

Чем отличается ток от напряжения? (2)

Связь тока и напряжения (0)

ИСТОЧНИК ПИТАНИЯ ДЛЯ АВТОМОБИЛЬНОГО РАДИОПРИЕМНИКА (0)

ЗАРЯДНОЕ УСТРОЙСТВО ДЛЯ АККУМУЛЯТОРА (0)

ЗАРЯДНОЕ УСТРОЙСТВО ДЛЯ ЛИТИЙ-НОННОГО ЭЛЕМЕНТА КОНТРОЛЛЕР ЗАРЯДНОГО УСТРОЙСТВА (0)

ОГРАНИЧИТЕЛЬ ЗАРЯДНОГО TOKA АККУМУЛЯТОРА (0)

ЗВУКОВОЕ УСТРОЙСТВО ДЛЯ ОХРАНЫ МОТОЦИКЛА (0)

функция

Выходной сигнал компаратора (A) по сравнению с выходным сигналом триггера Шмитта (B).

Триггер Шмитта работает аналогично аналоговому компаратору , но сравнивает входное напряжение и одно из двух возможных пороговых напряжений. Это превращает его в переключатель порогового значения : при превышении верхнего порогового напряжения выход неинвертирующей версии принимает максимально возможное выходное напряжение (HIGH); в виде двоичного числа, оно кодируется с 1 по положительной логике и 0 для отрицательной логики. Если напряжение падает ниже на нижнем пороге, выход принимает минимальное возможное выходное напряжение (LOW). Выходные напряжения между максимальным и минимальным значениями не возникают при статической работе.

И наоборот, с инвертирующим триггером Шмитта: если входное напряжение превышает верхний порог переключения триггера Шмитта, его выходное напряжение переключается с максимального значения напряжения на минимальное значение напряжения (LOW). Если входное напряжение затем падает ниже нижнего порога переключения, выходное напряжение снова переключается на максимальное выходное напряжение (ВЫСОКОЕ).

Два порога переключения разделены разницей напряжений, известной как гистерезис . При входном напряжении между пороговыми напряжениями выходное напряжение будет ВЫСОКИМ или НИЗКИМ в зависимости от предыдущей истории. Два порога переключения реализуются посредством обратной связи ( положительной обратной связи ) двоичного выходного напряжения на одном опорном напряжении, как известно из компаратора. В случае версий триггера Шмитта с дискретной структурой гистерезис может быть определен с помощью резисторов в структуре. Тогда оно может варьироваться от нескольких милливольт до значения выше напряжения питания. В триггерах Шмитта, которые выполнены в виде интегральной схемы , обычно невозможно изменить эти пороги переключения.

RS-триггер на логических элементах

Простейший способ его сделать – соединить вместе пару двухвходовых логических элементов И-НЕ. При этом обратная связь с выхода одного элемента подается на вход другого (см. схему ниже).

Как правило, в данной схеме входные сигналы показывают инверсными (с верхним подчеркиванием), хотя в дальнейшем при анализе работы используют обозначения прямых (неинвертированных) входов. Это сильно затрудняет понимание логики работы триггера. Поэтому мы не будем вводить инвертирование входов на этапе рассмотрения работы схемы на элементах И-НЕ, а учтем это в дальнейшем при ее модификации.

Сколько входов и выходов имеет RS-триггер? Из схемы выше видно, что он содержит S-вход и R-вход, которые служат, соответственно, для установки и сброса схемы, а также прямой Q и инверсный Q̃ выходы. Но данный простейший триггер относится к виду асинхронных, его условное обозначение показано ниже.

В синхронном устройстве имеется еще и вход C для тактовых импульсов.

Схема реализации d-триггера

В отличие от схем RS, данные устройства управляются с применением одного информационного входа. Это удобно, так как в двоичной системе один бит принимает только два значения (ноль или единицу). Кроме экономии проводников, такое решение помогает изменять задержку с применением регулировок частоты синхронизирующего сигнала.

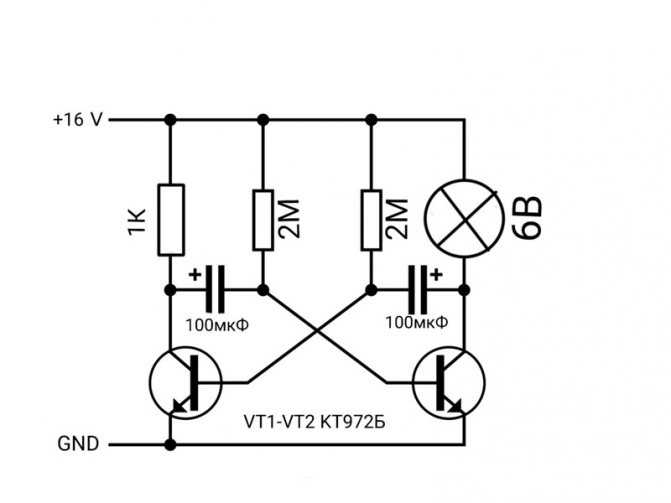

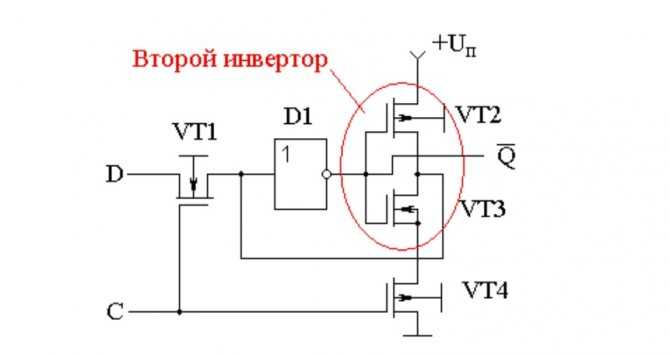

Схема реализации триггера на транзисторах

Вместо рассмотренных выше ТТЛ элементов для создания аналогичного устройства можно применить типовые транзисторы, созданные с применением КМОП технологии. На картинке изображен d триггер, принцип работы которого представлен ниже:

- при отсутствии сигнала на входе C транзистор VT1 находится в закрытом состоянии, не пропускает ток через полупроводниковый затвор;

- в этом состоянии не имеет значения уровень сигнала на D;

- если подать на С единицу, переход откроется;

- инвертор D1 обеспечит передачу на выход Q сигнала;

- два транзистора VT2 и VT3 образуют второй инвертор, который обеспечивает функционирование схемы в режиме типичного D триггера.

Таким образом, как и при работе с элементарными логическими компонентами, здесь данные состояния сохраняются только при нулевом уровне синхронизирующего сигнала. При увеличении его до уровня открытия полупроводникового перехода информация на входе и выходе будет повторяться с минимальной задержкой.

Для объективного анализа схемотехники надо изучить переходные процессы. Дело в том, что базовые для логических уравнений значения (ноль и единица) не всегда способны физически соответствовать идеальным значениям. Допустим, что управляющий сигнал поступает одновременно со сменой информационного. В этом случае триггер переходит в нестабильное состояние.

Ошибки проявляются в сбоях, когда последующие логические элементы ошибочно воспринимают амплитуду входных сигналов. Подобные ошибки могут блокировать полностью работу вычислительных устройств и другой техники.

Паразитные импульсные помехи образуют шумы в радиочастотном диапазоне. Состояние неопределенности увеличивает временные задержки при прохождении сигналов. Чтобы минимизировать вредное влияние и правильно делать конструкторские расчеты, производители триггеров указывают в сопроводительной документации минимальные допустимые параметры:

- setup time – промежуток перед синхронизирующим импульсом;

- hold time – длительность информационного сигнала.

Оценочный параметр MTBF показывает величину, обратно пропорциональную скорости отказов. Им определяют способность триггеров поддерживать стабильность рабочих процессов.

Триггер шмитта на транзисторах схема

В статье показано, каким образом, добавив цепь положительной обратной связи к паре Дарлингтона, можно создать триггер Шмитта с очень большим коэффициентом усиления тока (в типичном случае – 10,000). Я не знаю каких-либо решений, сравнимых по характеристикам, за исключением интегральных схем. Тем не менее, эта очень простая схема успешно выполняет универсальные функции. Схему можно рассчитать на работу с токами нагрузки от единиц миллиампер до ампер, причем при низких токах ее входное сопротивление может превышать 100 МОм.

На Рисунке 1 показана упрощенная схема в версии с входным NPN транзистором и активным низким уровнем, а на Рисунке 2 – с PNP транзистором и активным высоким уровнем. R2 и R3 (с учетом RL) задают напряжение на эмиттере Q1. Когда входное напряжение VIN возрастает от нуля до значения VIN(ON), определяемого выражением (1), Q1 начинает включаться. Возрастающий ток его коллектора, усиливаемый транзистором Q2, будет приводить к снижению выходного напряжения VOUT, вследствие чего напряжение на эмиттере Q1 будет уменьшаться, еще больше открывая транзистор. Процесс будет продолжаться до тех пор, пока Q1 не войдет в насыщение. Предполагается, что положительная обратная связь через резистор R3 больше, чем отрицательная, обусловленная током эмиттера Q1.

|

|

|

| Рисунок 1. | Триггер Шмитта на двух транзисторах. |

В этом и последующих уравнениях VBE и VCE с соответствующими индексами обозначают напряжения база-эмиттер и коллектор-эмиттер транзисторов Q1 и Q2.

| (1) |

Последнее иллюстрируется неравенством (2), которое должно выполняться, по крайней мере, с двукратным запасом. (В этой формуле β1 и β2 обозначают коэффициенты усиления токов транзисторов Q1 и Q2, соответственно, а RS – сопротивление источника сигнала VIN). Чем строже неравенство, тем большей будет величина гистерезиса.

|

|

(2) |

| (3) |

|

|

(4) |

| (5) |

| (6) |

Решая неравенство (2), можно, в соответствии с выражениями (3) и (4), определить границы допустимых значений сопротивления нагрузки RL и входного сопротивления RIN (в нашей схеме оно обозначено как R1). Кроме того, из (4) и (5) определяем граничное значение R3, которое должно быть, по крайней мере, в β2 раз больше, чем RL, чтобы сопротивление RIN было положительным. Типичное значение R3 не превысит половины от этой величины. Очевидно, что это будет справедливо, если коэффициент усиления Q2 велик. Выбрав R3 и VIN(ON), можно по формуле (6) рассчитать R2.

В состоянии «включено» напряжение VOUT приблизительно описывается выражением (7), где оно обозначено как VOUT(ON). Поскольку основной член выражения зависит от усиления Q2, измеренное напряжение обычно несколько отличается, но в типичном случае не выходит за пределы диапазона 2…3 В.

|

|

|

| Рисунок 2. | Версия с активным высоким уровнем. |

Ток, протекающий через RIN, увеличивает падение напряжения VR2 на резисторе R2 (уравнение 9), и если сопротивление R1 слишком мало, этот ток станет чрезмерно большим. (В предельном случае, если RIN равно 0, напряжение VOUT будет повторять VIN). При снижении входного напряжения VIN выход останется включенным до тех пор, пока Q1 не выйдет из насыщения. В этот момент положительная обратная связь выключит как Q1, так и Q2. Напряжение VIN(OFF), при котором этом произойдет, можно найти с помощью выражения (8). В связи с тем, что, скорее всего, вы захотите выбирать сопротивление R2, минимальным, чтобы минимизировать выходное напряжение низкого уровня, уровень VIN(OFF) будет зависеть от сопротивления резистора R1, но, опять же, значение VIN(OFF) зависит от коэффициентов усиления β транзисторов Q1 и Q2.